仭 僐傾儊儌儕丒僷僢働乕僕 仭

|

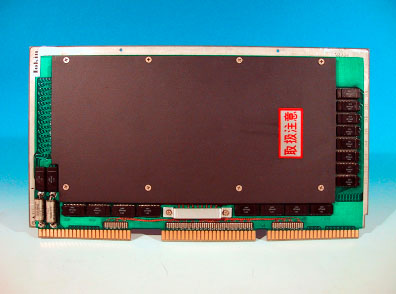

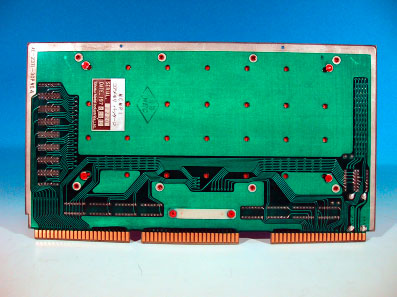

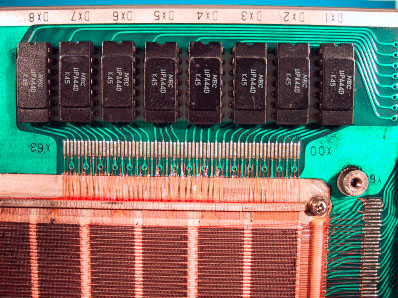

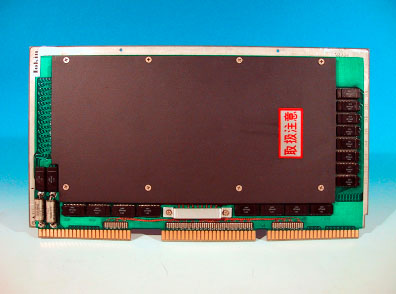

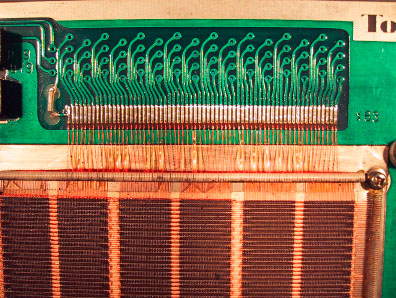

| 僐傾儊儌儕丒僷僢働乕僕婎斅乮昞柺乯 |

|

| 僐傾儊儌儕丒僷僢働乕僕婎斅乮昞柺丗僈乕僪傪奜偟偨偲偙傠乯 |

|

| 僐傾儊儌儕丒僷僢働乕僕婎斅乮棤柺乯 |

丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂搶杒嬥懏乮俿倧倠倝値乯惢俇係俲倐倝倲僐傾儊儌儕丒僷僢働乕僕丄俵俠俵俹俬

偱偁傞丅僐傾儊儌儕偲偼丄敿摫懱儊儌儕偑晛媦偡傞埲慜偵丄僐儞僺儏乕僞偺婰壇

慺巕偲偟偰梡偄傜傟偰偄偨傕偺偩丅崱偱偙偦俢俬俵俵婎斅侾枃偱俆侾俀俵俛偺梕

検傪帩偮惢昳偑堦斒揑巊傢傟偰偄傞偑丄偦偺愄丄儊儌儕偼旕忢偵崅壙偱梕検傕忣

偗側偄傎偳彫偝偐偭偨丅丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂僼僅儞丒僲僀儅儞巜摫偺傕偲偵惢嶌偝傟偨俬俙俽僐儞僺儏乕僞偼丄侾俋俆俀擭

偵壱摦傪奐巒偟偰偄傞偑丄偙偺儅僔儞偵偼係侽杮偺堿嬌慄娗抶墑憰抲偑儊儌儕偲

偟偰巊梡偝傟偰偄偨丅傑偨丄俤俶俬俙俠奐敪幰偺僄僢僇乕僩偲儌乕僋儕乕偑嶌惉

偟偨倀俶俬倁俙俠僐儞僺儏乕僞偵偼丄悈嬧憛傪巊梡偟偨壒嬁抶墑憰慄婰壇憰抲偑

儊儌儕偺栶妱傪壥偨偟偰偄偨丅僐傾儊儌儕偼偙傟傜懢屆偺婰壇慺巕傛傝偼廤愊壔

偝傟偰偄傞傕偺偺丄尰嵼巊梡偝傟偰偄傞敿摫懱儊儌儕偲偼慡偔堎側傞曽朄偱忣曬

傪拁偊偰偄偨傕偺偱偁傞丅丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂偙偙偵宖嵹偟偨僐傾儊儌儕丒僷僢働乕僕偼丄偍偦傜偔俶俤俠惢偺儊僀儞僼儗乕

儉偵搵嵹偝傟偰偄偨傕偺偺傛偆偱偁傞丅侾枃偺梕検偼俇係俲倐倝倲丅僇乕僪僄僢

僕僐僱僋僞傪夘偟偰丄昁梫側梕検暘偩偗僗儘僢僩偵憓擖偟偰憹愝偱偒傞傛偆偵側

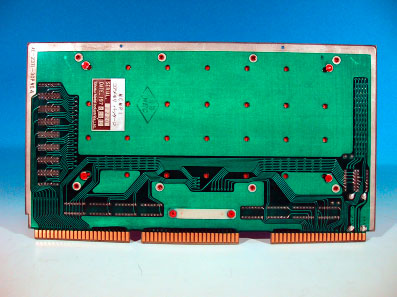

偭偰偄傞丅婎斅棤柺偵偼丄壓婰偺柫斉僔乕儖偑揬晅偝傟偰偄傞丅丂丂丂丂丂丂丂

丂丂俵俠俵俹俬丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂丂僐傾儊儌儕丂僷僢働乕僕丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂丂俽俤俼俬俙俴丏俀俀俀侽丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂丂俢俙俿俤丏侾俋俈係丏侽俋丏侾侽丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂丂俿倧倛倧倠倳 俵倕倲倎倢 俬値倓倳倱倲倰倝倕倱丆俴倲倓丏丂丂丂丂丂丂丂

|

| 婎斅棤柺偵揬晅偝傟偨柫斉僔乕儖 |

|

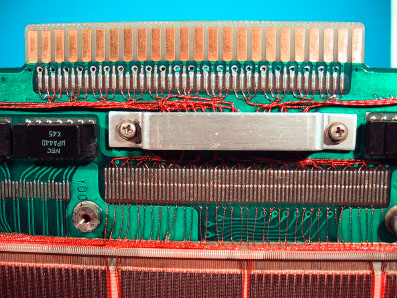

| 僇乕僪僄僢僕僐僱僋僞晹暘偺攝慄 |

丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

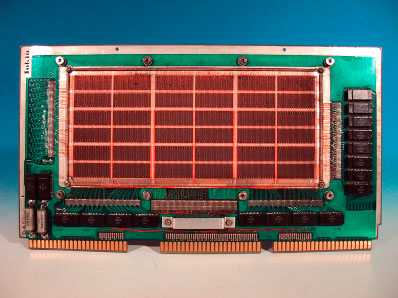

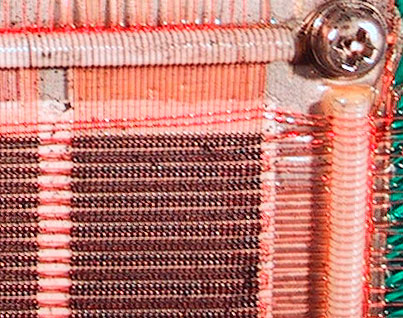

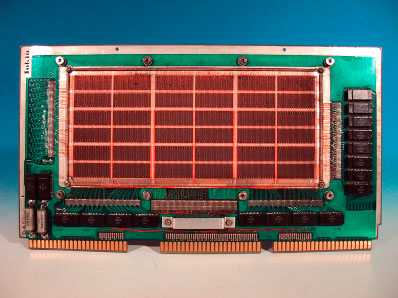

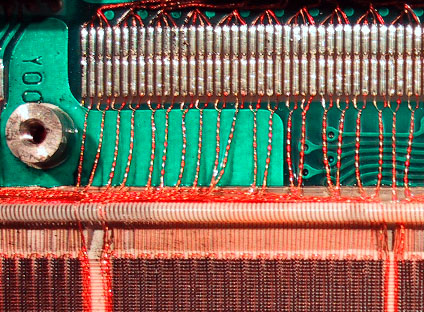

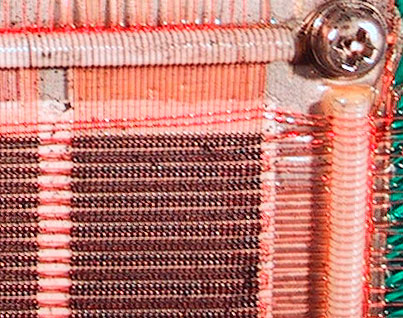

丂僐傾儊儌儕晹暘偼丄傾儖儈惢偺僈乕僪偱暍傢傟偰偄傞丅僱僕傪奜偟偰僈乕僪傪

庢傞偲丄俇亊俇偺儅僩儕僋僗忋偵攝抲偝傟偨儊儌儕僽儘僢僋偑尰傟傞丅僐傾儊儌

儕偼廲墶偵婯懃惓偟偔暲傫偩攝慄忋偵丄旕忢偵嵶偐偄僼僃儔僀僩僐傾偺儕儞僌傪

攝抲偟偨傕偺偱丄墦栚偵尒傞偲傑傞偱怐暔嵶岺偺傛偆偱偁傞丅僼僃儔僀僩僐傾偺

宍忬偼丄捈宎侽丏俁乣侾丏俆倣倣掱搙偺僪乕僫僣忬偱丄偙偺僐傾侾屄偵偮偒丄廲

偵侾杮丄墶偵俀杮偺揹慄偑娧捠偟偰偄傞丅僼僃儔僀僩僐傾偼丄揹慄偵棳傟傞揹棳

偺岦偒偵傛傝丄帴壔偺曽岦偑堎側傞丅僐傾偵塃夞傝偺帴懇偑惗偠偰偄傞偐丄嵍夞

傝偺帴懇偑惗偠偰偄傞偐傪悢帤偺乽侽乿偲乽侾乿偵抲偒姺偊偰丄忣曬傪婰壇偡傞

偺偑僐傾儊儌儕偱偁傞丅丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂杮僐傾儊儌儕僷僢働乕僕偺婎斅偺戝偒偝偼俀俉亊侾俆們倣丅偙偺偆偪丄儊儌儕

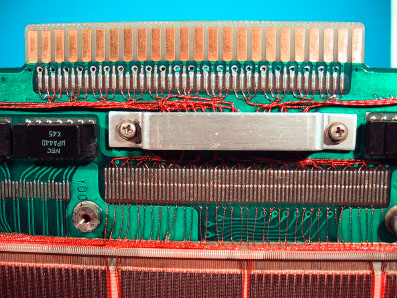

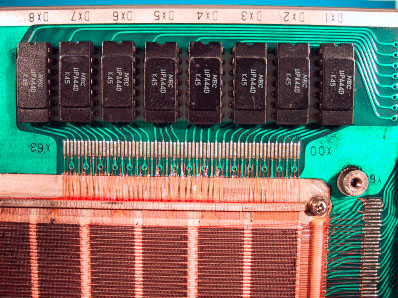

晹暘偺戝偒偝偼侾俉丏俆亊俋們倣掱搙偲側偭偰偄傞丅僇乕僪僄僢僕僐僱僋僞晹暘

偼丄俀係俹倝値偺抂巕偺傕偺偑俁偮暲傫偱偄傞丅僐僱僋僞偐傜婎斅撪晹傊岦偆攝

慄偼旕忢偵嵶偐偔丄敮偺栄傛傝傕嵶偄慄偑俀杮傛傝崌傢偝傟偰愙懕偝傟偰偄傞丅

偙偙傑偱偔傞偲丄岺寍昳揑側弌棃塰偊偩丅婎斅忋偵偼壓婰偺撴報偑偁傞丅丂丂丂

丂丂俙俤亅俀俁俈侾亅俁侽俹丂俶倧丏係丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂丂俿倧倠倝値丂俼倕倴俀俈丏丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

|

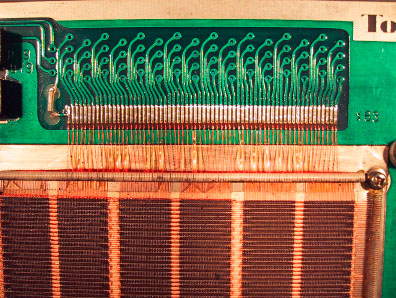

| 僐傾儊儌儕僽儘僢僋傊偺攝慄 |

|

| 傛傝崌傢偝傟偨揹慄偺傾僢僾 |

丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

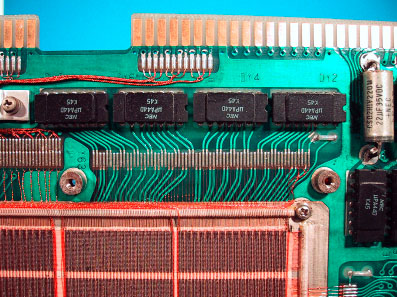

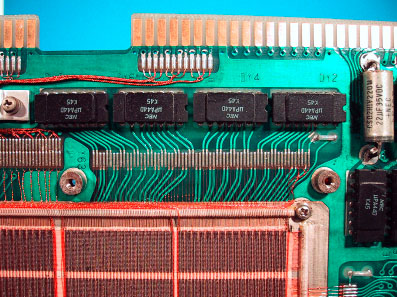

丂儊儌儕僽儘僢僋偺奜廃偵偼丄攝慄傪儅僂儞僩偡傞偨傔偺嵶偐偄傜偣傫忬偺僷僀

僾偑攝抲偝傟偰偍傝丄偦傟偧傟偺攝慄偼偙偺儅僂儞僩偐傜撪晹偵岦偭偰挘傜傟偰

偄傞丅儊儌儕僽儘僢僋偼丄僇乕僪僄僢僕懁偑倄幉丄偦傟偲悅捈曽岦偑倃幉偲側偭

偰偍傝丄倃丆倄偺儅僩儕僋僗偱嵗昗傪寛傔丄傾僪儗僗偲偟偰偄傞傛偆偩丅倄幉懁

偼丄侾丆俁丆俆丆俈偺婏悢僽儘僢僋偲俀丆係丆俇丆俉偺嬼悢僽儘僢僋偵暘棧偝傟

偰偍傝丄偦傟偧傟偺僽儘僢僋偵丄俶俤俠惢侾係俹倝値丂俢俬俹僷僢働乕僕偺丂丂

兪俹俙係係俢偑僶僢僼傽偲偟偰擖偭偰偄傞丅倃幉懁傕摨條偵俉偮偺僽儘僢僋偐傜

峔惉偝傟丄偦傟偧傟偵僶僢僼傽俬俠偑搵嵹偝傟傞丅側偍丄俢倃俋丄俢倄俋偺俀偮

偺僶僢僼傽偼丄偙傟偲偼暿偵愝偗傜傟偰偄傞偑丄偙傟偼僷儕僥傿價僢僩傪昞偟偰

偄傞傕偺偲巚傢傟傞丅丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂忋弎偟偨傛偆偵丄僐傾儊儌儕偼俇亊俇偺僽儘僢僋偵巇愗傜傟偰偍傝丄偦傟偧傟

偺僽儘僢僋傊偼旕忢偵嵶偐偄儚僀儎乕偑愙懕偝傟偰偄傞丅倃幉曽岦偺攝慄偼丄丂

倃侽侽乣倃俇俁傑偱偺俇係杮丄倄幉曽岦偺攝慄偼丄倄侽侽乣倄俇俁傑偱偺俇係杮

偱峔惉偝傟偰偄傞丅丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

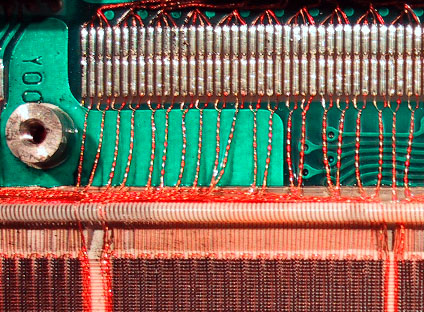

丂僼僃儔僀僩僐傾偦偺傕偺偼擏娽偱偼尒偊偵偔偄丅儖乕儁偱奼戝偡傞偲丄彫偝側

儕儞僌忬偺僐傾偑丄廲墶偵巤偝傟偨攝慄偺岎揰偵幬傔偵庢傝晅偗傜傟偰偄傞偺偑

妋擣偱偒傞丅杮摉偵偙偺傛偆側傕偺偱忣曬傪婰壇偱偒偨偺偐丄巚傢偢媈偭偰偟傑

偄偨偔側傞傛偆側僨僶僀僗偩丅丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

|

| 倃幉曽岦偺攝慄偵愝偗傜傟偨僶僢僼傽俬俠 |

|

| 倄幉曽岦偺攝慄偵愝偗傜傟偨僶僢僼傽俬俠 |

|

| 僼僃儔僀僩僐傾晹暘偺傾僢僾 |

丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

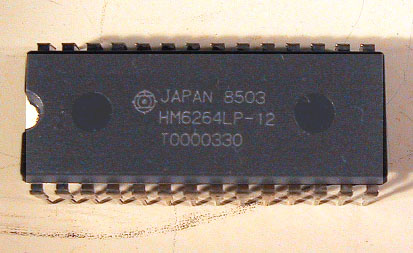

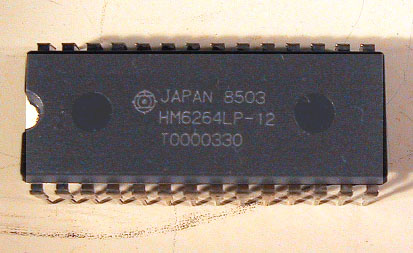

丂嵟屻偵丄偙偺僐傾儊儌儕丒僷僢働乕僕偲摨偠梕検傪敿摫懱儊儌儕僠僢僾偱峔惉

偟偨傜偳偆側傞偐丠傪帵偟偰偍偔丅壓婰偵宖嵹偟偨幨恀偼丄擔棫惢俽俼俙俵僠僢

僾丄俫俵俇俀俇係俴俹亅侾俀偱偁傞丅侾俋俉俆擭侽俁廡偺惢憿偱俀俉俹倝値偺俢

俬俹僷僢働乕僕丅偙偺俽俼俙俵偺梕検偼丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

俇係俲俛倝倲亖俇俆俆俁俇倐倝倲亖俉侾俋俀倐倷倲倕亖俉俲倐倷倲倕丂丂丂丂丂

偲側偭偰偍傝丄偙偺僐傾儊儌儕僷僢働乕僕偲摨偠偱偁傞丅宖嵹偟偨俽俼俙俵僠僢

僾偼偐側傝屆偄惢昳偱偁傞偑丄崱偲側偭偰偼俇係俲倐倝倲偺俽俼俙俵側偳丄梋傝

偵傕梕検偑彫偝偡偓偰巆偭偰偄側偐偭偨偨傔偩丅偲偵偐偔丄嫄戝側婎斅偵慇嵶側

嵶岺偱峔惉偟偨僐傾儊儌儕偼丄偙偺俁俆倣倣亊侾俀倣倣掱搙偺僾儔僗僠僢僋偺夠

偵廂傑偭偰偟傑偭偨偲偄偆偙偲偩丅丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂

|

| 偙偺僐傾儊儌儕偲摨梕検偺俽俼俙俵儊儌儕僠僢僾 |

亙 BACK